A major challenge in the design and verification of digital systems is the presence of race conditions.

These happen when several processes use common resources at once, which may result in strange or non-deterministic behavior.

Making sure that these problems are handled during hardware verification is essential to building dependable systems. The Universal Verification Methodology (UVM) provides robust design testing and efficient ways to prevent race conditions.

So, without prolonging, let’s take a look at how UVM avoids race conditions in hardware verification.

What Are Race Conditions?

A race condition happens when two or more processes access shared data concurrently, and at least one modifies it.

If the scheduling of these processes is unpredictable, the outcome can vary, leading to non-deterministic system behavior.

For example, if two processes try to write to a shared variable, the final value might depend on which process completes first, leading to errors if not handled correctly.

How UVM Avoids Race Condition?

UVM provides various techniques and instruments to reduce the possibility of race-related incidents:

1. Transaction-Based Modeling

UVM uses transaction-based communication between components. Instead of directly manipulating signals or states, components interact via abstracted transactions.

This ensures that concurrent access to shared data is minimized, as components do not directly interact with each other’s state.

For example, rather than having two processes modify the same shared signal, they pass transactions through a channel that handles the data exchange safely. This prevents simultaneous access to shared data.

2. Sequential Phases

In UVM, operations are broken down into predefined phases that control the simulation’s execution order.

These phases (such as build, run, and cleanup phases) ensure that actions are performed in a controlled, predictable sequence, which reduces the chances of concurrent accesses that could lead to race conditions.

During the run phase, for instance, UVM ensures that all processes run in parallel but in a managed and synchronized manner, helping avoid conflicts.

3. Synchronization Mechanisms

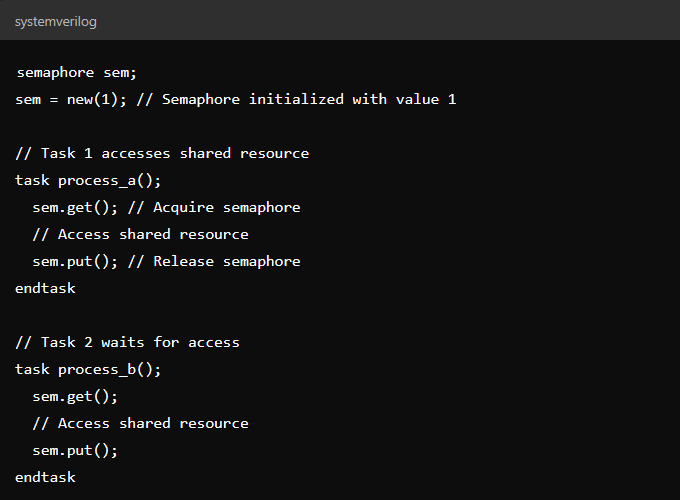

UVM offers various synchronization primitives like semaphores and events to control access to shared resources. These tools allow designers to coordinate the actions of multiple processes safely.

For example, semaphores are used to ensure that only one process can access a critical section at a time:

4. Configuration Database

UVM provides a configuration database to share settings and parameters among different components in a controlled manner.

The configuration database guarantees data consistency and prevents conflicts that may result from race conditions due to preventing direct access to shared variables.

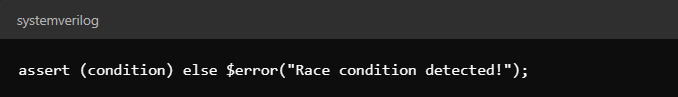

5. Assertions for Error Detection

UVM supports the use of assertions to catch issues like race conditions early in the simulation process. Designers can specify conditions that must hold true, and UVM will check for violations during the execution.

If a race condition is detected, the assertion can flag the issue immediately.

For example:

Practical Example: Avoiding Race Conditions in a Testbench

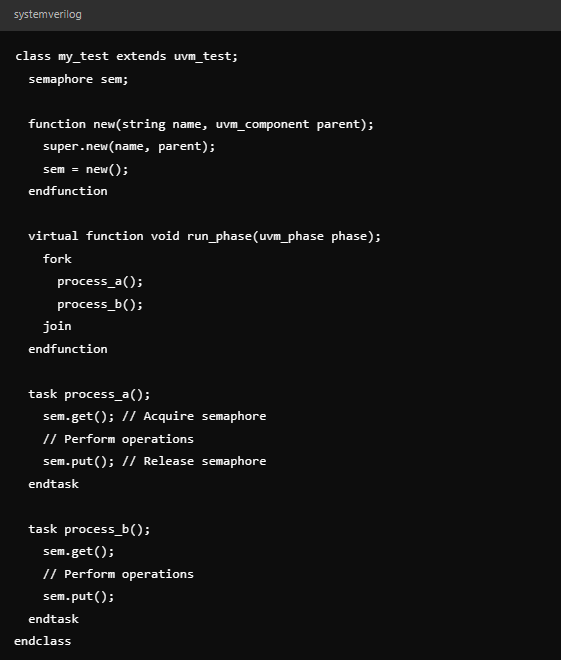

Here’s a simple example of how UVM handles multiple processes in a testbench to avoid race conditions:

In this example, both process_a and process_b use a semaphore to manage access to shared resources, ensuring that only one process can access the critical section at a time, thereby avoiding race conditions.

Conclusion

In order to prevent race situations, UVM provides an effective toolkit that makes sure hardware designs are rigorously tested and validated in a reliable and consistent way.

Designers can reduce the likelihood of race conditions and produce more dependable and effective hardware verification by utilizing concurrent execution phases, assertions, transaction-based modeling, and synchronization techniques.

We hope this guide helped you to understand how UVM avoids race conditions. If you enjoyed this article, make sure sure to check out our other technological articles, and share them with your colleagues!

We recommend the article on what is coding.